FPGA tehnologija pospešuje razvoj holografskih sistemov za shranjevanje podatkov

Tehnologija holografskega digitalnega shranjevanja podatkov (HDDS) je ena najobetavnejših pojavljajočih se tehnologij za optično shranjevanje podatkov, saj se tradicionalne tehnologije shranjevanja podatkov približujejo fizičnim mejam zmogljivosti.

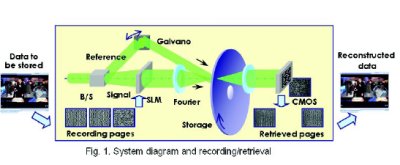

HDDS za razliko od tradicionalnih pristopov omogoča zelo visoko gostoto zapisa s kodiranjem podatkov znotraj prostornine medija, namesto samo na površini medija. Visoko prepustnost je možno doseči z zapisovanjem in branjem podatkov z uporabo velikih vzporednih pomnilniških blokov, ki se imenujejo strani, za razliko od branja ali zapisovanja enega bita naenkrat. Holografsko shranjevanje podatkov obljublja pospešitev prenosa podatkov na okoli milijardo bitov na sekundo (1 Gbps), zmanjšanje dostopnega časa na samo nekaj deset mikrosekund in povečanje gostote zapisa proti teoretičnemu maksimumu preko trilijona bitov na kubični centimeter (1 Tb/cm3).

Nedavno je Daewoo Electronics (Seul, Koreja) objavil namero, da izdela prvi prototip zelo natančnega servo nadzornega mehanizma za digitalno holografsko shranjevanje podatkov. Ocena stroškov izdelave prvotne izbire - izdelava prilagojene DSP plošče s tradicionalnim pristopom razvoja vgnezdenih sistemov - se je kmalu dvignila v deset tisoče dolarjev z nekajmesečnim rokom razvoja. Izziv pri tradicionalnem pristopu k razvoju je zelo serijski razvoj - razvijalci programske opreme čakajo na razvite strojne komponente, ponovitve načrtovanja pa so počasne. HDDS sistem je med prvimi svoje vrste in predstavlja precejšnje izzive v kompleksnosti načrtovanja. Da bi lahko prototip predstavili na trgu hitreje, je Daewoo uporabil novo generacijo orodij za grafičen razvoj sistemov (GSD - graphical system design) podjetja National Instruments (Austin, Texas). Grafičen razvoj sistemov je nova metodologija razvoja vgnezdenih sistemov, ki izkorišča prednosti enotnega, visokonivojskega grafičnega programskega jezika in prototipne platforme, ki temelji na programabilni FPGA strojni opremi, integriranih realnočasovnih procesorjih in priključljivih I/O modulih. Cilj GSD poteka načrtovanja je združevanje prototipne strojne opreme in poenostavljenih razvojnih orodij z namenom prečiščenja načrta sistema pred uporabo. To z odstranitvijo nizko nivojnih strojnih podrobnosti implementacije (kot so prenosi na ravni registrov) omogoča razvijalcem poenostavljanje kompleksnosti načrtovanja in izkoriščanje vgrajenih lastniških (IP) blokov za reševanje običajnih nalog, kot je nadzor gibanja in digitalno procesiranje signala.

Slika 1: Namesto dostopanja do enega bita naenkrat na površini medija, HDDS shranjuje in bere celotne strani informacij z več plasti v tridimenzionalnem mediju.

Slika 2: Platforme za hiter razvoj prototipov omogočajo načrtovanje prilagojene FPGA logike z uporabo grafičnega programiranja in vrednotenje vgnezdenih izdelkov z uporabo dejanskih I/O signalov.

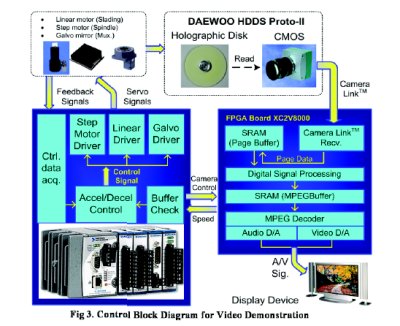

FPGA naprave so osrednja tehnologija za grafičen razvoj sistemov. FPGA naprava vsebuje matrico programabilnih logičnih vrat. Za razliko od procesorjev, FPGA naprave dobesedno preprogramirajo svoje notranje vezje za optimalno izvajanje procesorske logike. Omogočajo tudi natančno sinhronizacijo in usklajevanje, hitro odločanje in simultano izvajanje vzporednih nalog znotraj enega čipa, ki ga je preko ustrezne programske opreme možno v popolnosti programirati. Daewoo-jev HDDS prototip sestavljata dva glavna podsistema - elektro-optični nadzor gibanja, ki temelji na NI CompactRIO 3M FPGA šasiji in sistem za dekodiranje videa, ki temelji na 8M Xilinx FPGA plošči. CompactRIO sistem nadzoruje linearen motor, koračni motor, galvansko ogledalo in CMOS kamero. Vsaka nadzorna zanka za gibanje zahteva natančen nadzor. Zato se povratni signali s senzorjev uporabljajo za implementacijo nadzora z zaprtimi zankami neposredno v FPGA strojni opremi. Z implementacijo nadzornih zank v strojno opremo je popolnoma odstranjen časovni zamik. S tem je hitrost delovanja nadzorne zanke omejeno samo s hitrostjo osveževanja I/O modulov.

Za razliko od tradicionalnih računskih plošč je CompactRIO dovoljeval Daewoo-ju prilagoditev točnosti pulznega generatorja na resolucijo enojnega FPGA urnega cikla z uporabo NI LabVIEW FPGA Module programske opreme. Da bi odstranili "drsenje" so načrtovalci razvili kompleksne algoritme za nadzor motorja z uporabo prilagojenih matematičnih funkcij za pospeševanje in zaviranje. Poleg nadzora gibanja, komunicira CompactRIO še s FPGA ploščo za dekodiranje videa, ki so jo za zajemanje videa in nadzor CMOS kamere razvili z uporabo NI tehnologije za obdelavo signala. CompactRIO ravno tako nadzira spreminjajočo se prenosno hitrost podatkov s preverjanjem količine podatkov, ki se zbirajo v predpomnilniku MPEG dekoderja. Byoungbok Kang, inženir za načrtovanje pri Daewoo Electronics poroča: „Namesto da bi porabili na deset tisoče dolarjev in nekaj mesecev za razvoj prilagojene DSP plošče je bila naša ekipa zmožna razviti ta revolucionarni HDDS sistem hitro in ekonomično z uporabo hitre NI CompactRIO FPGA tehnologije in NI LabVIEW programske opreme. Presenetilo nas je, da je možno tak projekt zaključiti tako hitro in učinkovito. Z uporabo orodij NI grafičnega razvojnega sistema je lahko Daewoo razvil svoj sistem s proračunom nekaj tisoč dolarjev brez odrekanja na strani zmogljivosti. Nadaljnje se je razvojni cikel skrčil na samo en mesec, kar je industriji sistema prineslo priporočilo pri prvi javni predstavitvi na Korea Electronics Show-u (KES) v oktobru 2005.

Na FPGA osnovane nadzorne zanke omogočajo hiter nadzor gibanja po več oseh z uporabo prilagojenih algoritmov za pospeševanje in zaviranje. Z implementacijo nadzornih zank v strojno opremo je hitrost omejena samo s hitrostjo osveževanja I/O modulov.

Več informacij: http://www.icm.si/sejmi/novice_newsletter.php